### **Features**

- 48 Pattern channels

- 1 ns sample resolution 20,000 samples per channel <10 ps channel to channel RMS jitter 80 ps channel to channel skew

- Channel Output

LVDS logical level

1 ns rise & fall time

- Trigger sources: External, Internal or Optical

- Analog, Digital and optical I/O

- Controlled via front panel, Ethernet or Webpage

## **Applications**

- FPGA, ASIC emulation and simulation

- Production test

- Digital stimulus

- Control of multiple high power pulsers

- · Big physics application

- Automatic Test Equipment

## **Description**

The GFT7048 is a 48 Channel Digital Pattern Generator that operates either as a standalone device, or as a component in a timing system. In a timing system, the GFT7048 is operated in conjunction with a GFT3001 Master Transmitter that controls and synchronizes several GFT7048 DPGs via optical fibers ( for more information about timing system ask to factory)

The generator provides two trigger modes: External mode from trigger input or internal mode from one frequency programmable generator

One "T0" channel is used as a time reference for all the LVDS channel Outputs.

A global delay up to  $10 \mu s$  may be used to control skew between GFT7048 in a timing system configuration (optical network compensation).

A fine delay function (<50 ps resolution) on each channel pattern may be used to adjust skew between pattern channels.

Eight (8) data patterns of 48 channels can be set and saved in the generator. Each pattern channel is 20,000 samples of 1 ns resolution ( $20 \mu s$  total length).

Seventeen (17) Analog and Digital I/O may be used to control and monitoring some devices of your application (high voltage power supply, sensor, switch ...).

GFT7048 parameters can be locally controlled over the front panel keys and LCD display, and remotely controlled via Ethernet (10/100/1000 Mb/s) or Internet (web page from internal web server).

The GFT7048 is low profile 19", 2U rack mountable instrument.

**Application**: This Digital Pattern Generator is well suited for FPGA or ASIC simulation or emulation, production test, digital stimulus and application where speed, resolution, channel number are critical.

# **Specifications**

| 48 Pattern channels                          |                                                |  |  |

|----------------------------------------------|------------------------------------------------|--|--|

| Sample Resolution                            | 1 ns (1 GS/s)                                  |  |  |

| Sample Nesolution  Sample number per channel | 20,000                                         |  |  |

| Skew (Channel to channel)                    | < 80 ps (between first bits)                   |  |  |

| Drift (Channel to channel)                   | < 100 ps pk-to-pk (first bits) @ 25°C (24h)    |  |  |

|                                              | < 300 ps pk-to-pk (first bit) @ 20-30°C (24h)  |  |  |

| Jitter (Channel to channel)                  | < 10 ps RMS                                    |  |  |

| Channel LDVS Outputs (T1-T48)                |                                                |  |  |

| Logical level type                           | LVDS                                           |  |  |

| Differential voltage                         | 350 mV typ.                                    |  |  |

| Required load                                | 100 Ω                                          |  |  |

| Rise/fall time                               | <1 ns                                          |  |  |

| Connectors                                   | 3 x SAMTEC p/n ERI8-031-S-D-RA + ERC-031-01-02 |  |  |

| Internal Time base                           |                                                |  |  |

| Frequency                                    | 1 GHz                                          |  |  |

| Stability                                    | ±0.28 ppm                                      |  |  |

| Clock Input                                  |                                                |  |  |

| Required level                               | >0.3 V pk-to-pk, AC                            |  |  |

| Absolute maximum level                       | 2.8 V pk-to-pk                                 |  |  |

| Required frequency                           | 10 MHz +/-0.1 kHz                              |  |  |

| Impedance                                    | 50 Ω                                           |  |  |

| Connector                                    | BNC                                            |  |  |

| Clock Output                                 | 5110                                           |  |  |

| Level                                        | >2 V pk-to-pk AC on 50Ω load                   |  |  |

| Shape                                        | Square                                         |  |  |

| Frequency                                    | 10 MHz                                         |  |  |

|                                              |                                                |  |  |

| Rise/fall time                               | <10 ns                                         |  |  |

| Connector                                    | BNC                                            |  |  |

| TO Output                                    |                                                |  |  |

| Function                                     | Time reference                                 |  |  |

| Shape                                        | Square                                         |  |  |

| Level                                        | +10 V ± 0.5V                                   |  |  |

| External load                                | 50 Ω                                           |  |  |

| Rise time                                    | <2 ns                                          |  |  |

| Width                                        | 100 ns to 10 μs (6.25 ns resolution)           |  |  |

| T0 to DP outputs, skew                       | <+/- 3.125 ns (Global delay set to 0)          |  |  |

| To to DP outputs, jitter                     | <25 ps RMS (internal or optical trigger)       |  |  |

| Connector                                    | BNC                                            |  |  |

| External Trigger Input                       | 20                                             |  |  |

| Required level                               | > + 1V                                         |  |  |

| Maximum level                                | + 10 V                                         |  |  |

|                                              |                                                |  |  |

| Repetition rate                              | Up to 10 kHz                                   |  |  |

| Impedance                                    | 50 Ω                                           |  |  |

| Connector                                    | BNC                                            |  |  |

| Latency                                      | <200 ns (trigger input to channel output)      |  |  |

## **Specifications (cont'd)**

| Internal trigger                      |                                                |  |  |  |

|---------------------------------------|------------------------------------------------|--|--|--|

| Programmable generator                |                                                |  |  |  |

| Global delay                          |                                                |  |  |  |

| Function                              | Control skew between GFT7048                   |  |  |  |

| Range                                 | 0 to 10 μs                                     |  |  |  |

| Resolution                            | 6.25 ns                                        |  |  |  |

| Fine delay                            |                                                |  |  |  |

| Function                              | Control skew on each channel                   |  |  |  |

| Range                                 | 1.1 ns                                         |  |  |  |

| Resolution                            | <50 ps (T1 to T48)                             |  |  |  |

| Pattern Memory                        |                                                |  |  |  |

| Pattern memory size                   | 48*20,000 samples                              |  |  |  |

| Pattern number                        | 5 User Patterns (user configurable)            |  |  |  |

|                                       | 3 Test Patterns (fixed)                        |  |  |  |

| Analog I/O (3 inputs, 3 outputs)      |                                                |  |  |  |

| Туре                                  | ADC (inputs), DAC (outputs)                    |  |  |  |

| Resolution                            | 12 bits                                        |  |  |  |

| Level                                 | 0 - 10 V                                       |  |  |  |

| Connector                             | 25 pin D-Sub type plug                         |  |  |  |

| Digital I/O (4 inputs, 4 outputs)     |                                                |  |  |  |

| Level                                 | +24V isolated                                  |  |  |  |

| Input to output, voltage insolation   | 5000 V <sub>RMS</sub>                          |  |  |  |

| Connector                             | 25 pin D-Sub type socket                       |  |  |  |

| Safety optical I/O (1 input, 2 output | es)                                            |  |  |  |

| ARM and STATUS outputs                |                                                |  |  |  |

| Shape                                 | Square                                         |  |  |  |

| Level                                 | >-9 dBm                                        |  |  |  |

| Wavelength                            | relength 850 nm                                |  |  |  |

| INH input                             |                                                |  |  |  |

| Function                              | All the channel outputs may be inhibited       |  |  |  |

| Threshold                             | >-15 dBm                                       |  |  |  |

| Wavelength                            | 850 nm                                         |  |  |  |

| User Interface                        |                                                |  |  |  |

| Front panel                           | 2x20 character LCD display + keys + indicators |  |  |  |

| Ethernet 10/100/1000 Mb/s             | SCPI commands and Web page                     |  |  |  |

|                                       | RJ45 Connector                                 |  |  |  |

| General                               |                                                |  |  |  |

| Power voltage                         | 90 to 240 VAC                                  |  |  |  |

| Power consumption                     | 70 W                                           |  |  |  |

| Weight                                | <15 kg (< 33 lbs)                              |  |  |  |

|                                       | <13 kg (< 33 lbs)                              |  |  |  |

## GFT7048

## **48 Channel Digital Pattern Generator**

### **Functional Overview**

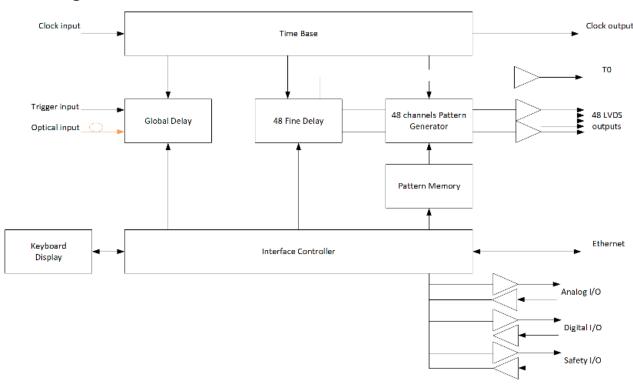

#### **Block diagram**

The GFT7048 includes the following functions:

#### **Time Base:**

GFT7048 can run three modes for the clock reference:

- Internal: Time base and internal clocks are synthetized from an onboard 10 MHz VCTCXO.

- External: the internal clocks and time base are synthetized from an external 10 MHz input (Clock input).

- Optical: the internal clocks and time base are synthetized from the reference clock decoded from the optical serial data stream reception (160 MHz).

#### **Global Delay**

A global delay up to 10  $\mu$ s may be used to control skew between GFT7048 in a timing system configuration (optical network compensation).

#### **48 Fine Delay**

A fine delay (<50 ps resolution) may be used to adjust skew between pattern channels.

#### 48 channel pattern generator

They are 48 independent channels pattern generator. Content of the pattern is stored in pattern memory. "T0 output" channel is used as a time reference (delay = 0) for all 48 LVDS outputs.

#### **Pattern Memory**

GFT7048 can memorize up to 8 different data pattern of 48 channels. Five are user configurable and three are test patterns.

#### **Channel LVDS outputs**

The outputs are specially designed to provide LVDS level via high speed SAMTEC connectors.

#### Analog, digital and safety I/O

This I/O lines under software command allow to control and monitoring other external devices. **Interface Controller:** It manages internal functions and user interfaces. The parameters can be locally controlled over the front panel keys, and remotely displayed and controlled via Ethernet (10/100/1000 Mb/s) or Internet (web page from internal web server)

### **Control and Software Tools**

They are three ways to control the generator:

- <u>"local way"</u> via the front Panel Display an Keyboard. This way allows to locally configure the settings (delay, trigger source, time base reference...), control operation and display status of the generator.

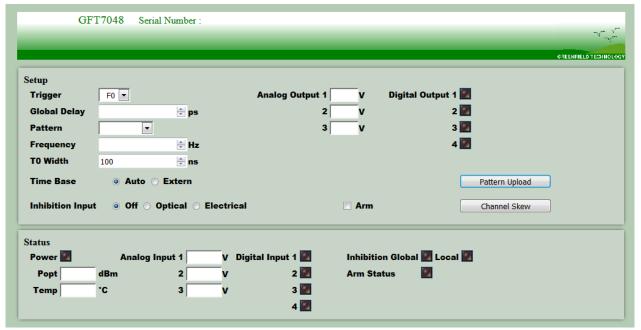

- "Easy remote way" via Internet and control panel web pages on your PC. Web page, from embedded Web server, provides a simple method to configure settings (delay, trigger mode, trigger source, time base reference...) to control operation, to upload user pattern and to display the status of the instrument. The configuration information of the instrument is stored and saved in the GFT7048.

The web page can be opened via Internet Explorer, Mozilla Firefox or Chrome. After connecting a cable from the GFT7048's Ethernet port to your computer Network, enter the GFT7048's IP address into your PC's browser (the IP address can be identified or assigned via the front panel). The browser will automatically open the control panel web page on your PC.

Setup Web page

"General remote way" via LabVIEW software application or other PC software application.

### **Front and Rear Panel**

Front Panel

Digital Pattern Outputs

Ethernet

Rear Panel

### **Connector, Switch, Indicators**

| Front | Panel                                              | <b>Rear Panel</b> |                                    |

|-------|----------------------------------------------------|-------------------|------------------------------------|

| •     | Indicators                                         | LAN               | LAN connection: RJ45 connector     |

| PWR   | Power supply ON (green)                            | OPT               | Optical input: SC/APC connector    |

| LAN   | LAN connected / unconnected (yellow)               | ARM               | ARM output: ST connector           |

| OPT   | Timing system sync. / unsync. (blue)               | STATUS            | STATUS output: ST connector        |

| F0    | Blinks at the trigger event F0 if selected (blue)  | CLK IN            | Clock input: BNC connector         |

| SS0   | Blinks at the trigger event SS0 if selected (blue) | CLK OUT           | Clock output: BNC connector        |

| SS1   | Blinks at the trigger event SS1 if selected (blue) | T0                | T0 output: BNC connector           |

| SS2   | Blinks at the trigger event SS2 if selected (blue) | T1 to T16         | Digital pattern outputs: SAMTEC    |

| SS3   | Blinks at the trigger event SS3 if selected (blue) | T17 to T32        | connector                          |

| SS4   | Blinks at the trigger event SS4 if selected (blue) | T33 to T48        |                                    |

| •     | Small keyboard for local control                   | TRIG IN           | External Trigger Input: BNC        |

|       |                                                    |                   | connector                          |

| •     | Display for local control                          | INH               | Inhibition input: BNC connector or |

|       |                                                    |                   | ST connector                       |

|       |                                                    | Digital I/O       | Digital I/O: D-SUB 25 pin socket   |

|       |                                                    | Analog I/O        | Analog I/O: D-SUB 25 pin plug      |

|       |                                                    | LINE IN           | AC power plug (90-240 VAC) and     |

|       |                                                    |                   | power ON/OFF switch                |

## **Ordering Information**

Digital Pattern Generator part number is: GFT7048